Main menu

You are here

DDS zum selbermachen

1. Motivation

Beim durchstöbern des WWW bin ich unter anderem auf ein Projekt gestoßen, das sich sinngemäß a poor-mans DDS nannte ([1]). Verwendet wurde ein kleiner Microcontroller von Atmel ([2]) sowie als DA-Wandler ein paar Widerstände. Gesteuert wurde das ganze über die serielle Schnittstelle vom PC aus. Da mir die Angelegenheit ganz gut gefallen hat, habe ich beschlossen, das auch mal anzugehen.

In diesem ersten Teil, bestand mein Ziel darin,

- den dahinterstehenden Algorithmus zu verstehen

- ihn zu implementieren

- und daraus vielleicht einen kleinen Signalgenerator zu bauen.

2. Das Konzept

Zunächst muß vorausgeschickt werden, daß es für diese Zwecke natürlich fertige integrierte Schaltkreise, vornehmlich von Analog Devices ([3]) gibt, die einen DDS-Signalgenerator mit Ausgangsfrequenzen im 100 MHz-Bereich und höher haben. Diese Bausteine sind zwar nicht billig, aber sie sind auf jeden Fall die bessere Wahl. Daher sehe ich dieses Projekt eher unter didaktischen Aspekten. Bei Analog Devices findet man übrigens auch einen guten Grundlagenartikel ([4]). Auch Wikipedia beschreibt das Konzept von DDS, der direkten digitalen Synthese bzw. der direct digital synthesis kurz ([8]).

Zunächst einmal sollte alles notwendige auf ein Steckbrett aufgebaut werden können. Damit fallen schon mal SMD-Halbleiter weg. Als Prozessor sollte ein Atmel ATTiny2313 ([5]) und alternativ ein Microchip PIC16F628A ([6]) zum Einsatz kommen, da ich diese beiden Exemplare gerade vorrätig hatte. Die Variante mit dem PIC-Prozessor wird hier aber nicht weiter diskutiert. Die Frequenzeingabe soll über einen Drehgeber erfolgen. Die Ausgabe über ein kleines vierstelliges Display, SLR2016 von Osram ([10]). Die DA-Wandlung soll einem fertigen Wandler, ZN428 ([7]), überlassen werden. Alles Teile, die sich in der sprichwörtlichen Bastelkiste angesammelt haben.

Die Software ([9]) besteht im wesentlichen aus zwei Teilen: 1. Eine Interrupt-Service-Routine. die in gleichmäßigen Intervallen aufgerufen wird, und den jeweils nächsten auszugebenden Wert auf den DA-Wandler gibt. 2. Das Hauptprogramm übernimmt die Initialisierung sowie die Abfrage des Drehgebers und die Berechnung der Parameter. Außerdem wird die Ausgabe vorbereitet.

Das Verfahren DDS, dessen Buchstaben für Direct Digital Synthesis, also direkte digitale Synthese stehen, erzeugt das Ausganssignal, das in der regel ein Sinus-Signal ist, rein numerisch. Daher fällt DDS auch in die Gruppe der NCO, numerically controlled oscillators, also den numerisch gesteuerten Oszillatoren. Andere Formen von Oszillatoren sind natürlich freischwingende Oszillatoren, die sich in ihrer Frequenz mittels Kapazitätsdiode variieren lassen, sowie Quarzoszillatoren oder Keramik-Resonatoren, deren Frequenz fest und vor allem bei Quarzoszillatoren ausgesprochen stabil ist. Kombiniert man einen freischwingenden Oszillator und einen Quarzoszillator mit einstellbaren Frequenzteilern und einem Phasendiskriminator in geeigneter Weise, so erhält man einen PLL-Oszillator, der sich dadurch auszeichnet, daß die Phasenlage des freischwingend Oszillators über eine Regelung an die Phase des Referenzoszillators gekopelt wird. PLL steht für Phase Locked Loop, also eine phasengekoppelte (Regel)schleife. Auch diese Oszillatoren sind natürlich mittels eines Steuerwortes in der Frequenz einstellbar. Allerdings dauert es immer eine gewisse Zeit, bis die Regelung sich auf die neue Frequenz eingestellt hat. Außerdem ist die kleinste Schrittweiter so groß wie die Referenzfrequenz. Typischerweise einige 10 kHz. Nur mit mehreren Regelschleifen gelangt man zu Schrittweiten in der Größenordnung Hz.

DDS benötigt keine Einschwingzeit für eine Regelung und die Schrittweite liegt bereits bei einfachsten Ausführungen im Sub-Herz Bereich. Herzstück ist der sogenannte Phasenakkumulator, der nichts weiter ist, als ein Addierer, der in jedem Taktzyklus einen vorgegebenen Wert aufaddiert. Der Wert 0 des Phasenakkumulators steht für die Phasenlage von 0 Grad. Sein Maximalwert+1 steht für 360 Grad. Daraus ersieht man, daß mit jedem Taktzyklus eine neue Phasenlage des Ausgangssignals, unabhängig von dessen Frequenz vorliegt. Die Phase muß nur noch umgerechnet werden in einen Amplitudenwert. Bei einem Sinussignal ist zur Phase 0 die Amplitude ebenfalls 0, zur Phase 90 Grad ist sie +1, bei 180 Grad wieder Null und bei 270 Grad -1. Der numerische Wert der Amplitude wird dann schließlich auf einen DA-Wandler gegeben, um ein Ausgangssignal zu erzeugen.

Beispiel 1: Der Phasenakkumulator kenne nur Werte zwischen Null und 359. Sein Wert steht also direkt für die aktuelle Phasenlage. Mit jedem Schritt werde um eine Einheit weitergeschaltet. Damit erhält man ein sinusförmiges Signal, dessen Frequenz ein 360stel der Taktfrequenz des Phasenakkumulators ist. Wird jeweils zwei Einheiten weitergeschaltet, dann verdoppelt sich die Ausgangsfrequenz.

Beispiel 2: Der Phasenakkumulator hat 16 bit; kann also den Zahlenbereich zwischen Null und 65535 darstellen. Die Taktfrequenz des Phasenakkumulators sei 65536 Herz. Damit ist die kleinste darstellbare Frequenz 1 Herz. Die maximal sinnvoll nutzbare Frequenz liegt bei 30 bis 40% der Taktfrequenz. Gemäß Shannon ist sowieso bei der halben Taktfrequenz schluß, da darüber die Ausgangsfrequenz wieder abnimmt.

Handelsübliche DDS-Bausteine haben Phasenakkumulatoren mit 32 bis 40 bit Auflösung bei einer Taktfrequenz bis zu 300 MHz. Die Auflösung liegt dabei immer noch im mHz (Milli-Hertz!)-Bereich. Man kann damit also Sinus-Generatoren bauen, die am Stück von 0 bis über 100 MHz in Schritten von 0.001 Hz durchstimmbar sind. Mit herkömmlichen Mitteln (PLL) sind solche Signalquellen nicht darstellbar.

3. Der Prototyp

Das folgende Bild zeigt den Prototyp:

Vorne links befindet sich das vierstellige Display, hinten mitte der Quarzoszillator für 20 MHz, hinten rechts ein OP-Verstärker, vorne mitte der DA-Wandler und vorne rechts der ATTiny 2313. Außerdem sieht man noch einen kleinen Lautsprecher, um das Signal hörbar zu machen sowie den Drehgeber ganz vorne rechts.

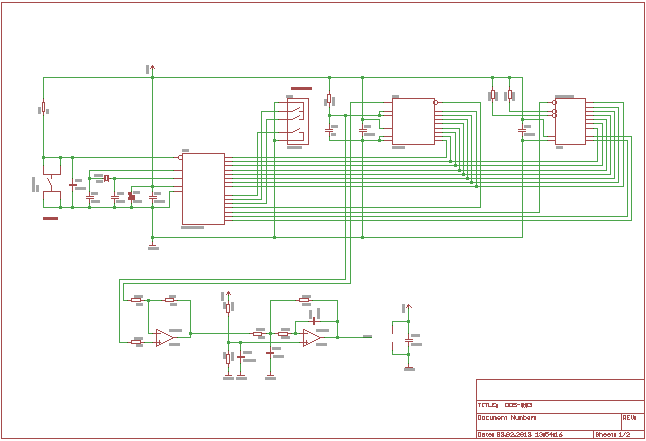

Hier folgt dann noch der Schaltplan, der in voller Auflösung angezeigt werden kann, wenn man ihn anclickt:

Man erkennt im Schaltplan wieder die Komponenten, die auch auf dem Steckboard vorkommen: Der Controller, der Drehgeber, der DA-Wandler, das vierstellige Display und der OP-Verstärker. Der Schaltplan weicht allerdings in einigen Kleinigkeiten vom Aufbau auf dem Steckbrett ab. Auf dem Steckbrett wurde ein separater Quarzoszillator mit 20 MHz verwendet während im Schaltplan der Oszillator des Controllers mit einem 20 MHz-Quarz verwendet wird. Im Schaltplan kommt ein Reset-Taster vor, der auf dem Board nicht existiert. Der Drehgeber im Schaltplan hat noch einen weiteren Kontakt (1,2), der ebenfalls auf dem Steckboard nicht verwenet wird. C17 gibt es auf dem Board nicht. Manche Bauteile entstammen der Bastelkiste und haben daher etwas ungewohnte Werte - etwa C16 mit 340 pF.

Ein Layout wurde nicht vorgesehen; für das Experiment war es ausreichend, daß die Schaltung auf dem Steckbrett aufgebaut werden konnte.

4. Ergebnisse

Das folgende Bild zeigt nochmal den Aufbau zusammen mit dem Schirmbild des Oszilloskops. Die Ausgangsfrequenz beträgt 1183 Hz, wie man mit Mühen ablesen kann.

Hier noch ein Oszillogramm, auf dem man ein wenig die 'Unruhe' im Signal sieht, die einerseits von der Auflösung des DA-Wandlers (8 bit) und andererseits von der Taktfrequenz des Phasenakkumulators (hier ca. 50 kHz) herrührt.

Die Experimente mit dem PIC-Prozessor verliefen ebenfalls erfolgreich. Jedoch lag die maximale Ausgangsfrequenz bei vergleichbarer Taktfrequenz mit dem Atmel-Prozessor nur bei rund der Hälfte.

5. Referenzen und Links

- [1]: Mini DDS

- [2]: Atmel: AVR 8-bit RISC

- [3]: Analog Devices

- [4]: Analog Devices: A Technical Tutorial on Digital Signal Synthesis (PDF)

- [5]: Atmel: Produktübersicht: ATtiny2313

- [6]: Microchip: Produktübersicht: PIC16F628A

- [7]: GEC PLESSEY: Datenblatt: ZN428 (PDF)

- [8]: Wikipedia: Direct Digital Synthesis, DDS

- [9]: Source Code für den ATiny2313

- [10]: Vierstelliges intelligentes Display