Hauptmenü

Sie sind hier

Der Vorteiler

Hier ist nicht der Vorteiler gemeint, der etwa ein zu messendes Signal bei 1 GHz auf eine Frequenz z.B. unter 10 MHz herunterteilt, sondern der Vorteiler, der den Referenztakt von 10 MHz auf 10 kHz reduziert. Die Ablaufsteuerung wird den Takt weiter herunterteilen so daß Torzeiten zwischen 0.01 und 10 Sekunden verfügbar sind.

Der Vorteiler ist relativ einfach, weswegen ich ihn am Anfang präsentieren. Er soll also ein 10 MHz-Signal auf 10 kHz herunterteilen. Er wird daher einen Eingang namens clk haben und einen Ausgang, den ich mit clk1000 (1000 steht für 1/1000) bezeichne. Darüber hinaus gibt es einen reset-Eingang (reset) und einen enable-Eingang (en). Im folgenden der VHDL-Code:

Ohne den code im einzelnen erklären zu wollen sei erwähnt, daß die entity prescaler genau die oben aufgeführten Ein- und Ausgänge besitzt und daß intern ein 9 bit breiter Zähler verwendet wird. Er beginnt bei Zählerstand 499 rückwärts bis auf Null zu zählen und invertiert dann beim Vesuch auf -1 zu zählen c_int. Außerhalb der synchronen Umgebung p1 wird der Zustand von c_int direkt an clk1000 in einem nebenläufigen Prozeß weitergereicht. Nachfolgend noch die Constraints, die die Pinbelegung festlegen.

Der Vorteiler wurde auch simuliert. Das folgende File zeigt den Simulationsaufbau.

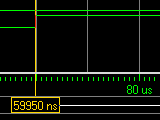

Initial sind alle Eingänge auf Low. Der Augang ist anfangs undefiniert. Simuliert wird mit einer Taktfrequenz von 10 MHz. Das Reset-Signal (active high) geht nach 3 us für 3 us auf High um danach für den Rest der Simulation auf Low zu verbleiben. Das enable-Signal (evenfalls active high) geht nach 10 us bis zum Ender der Simulation auf High. Ab diesem Zeitpunkt wird das Eingangssignal mit 10 MHz Taktfrequenz durch 1000 geteilt. Das folgende Bild illustriert das Simulationsergebnis:

Die oberste Spur zeigt das 10 MHz-Signal, das bei dem gewählten Zeitfenster nicht mehr aufgelöst dargestellt wird. Daher der breite grüne Balken. Darunter ist das enable Signal dargestellt, gefolgt vom Reset-Signal. Gemessen wurde nun der Abstand zweier aufeinanderfolgender steigender Flanken des Ausgangssignals clk1000. Schon die automatische Abstandsmessung der beiden Cursorlinien zeigt 100,000,000 ps an, was, nach auszählern der Nullern genau 100 us entspricht und das ist nichts anderes als 10 kHz. Dieses CPLD müßte schon mal funktionieren und tut es auch, nachdem es auf dem Experimentierboard programmiert worden ist.